An AMD Update: Fab 36 Begins Shipments, Planning for 65nm and AM2 Performance

by Anand Lal Shimpi on April 4, 2006 11:00 AM EST- Posted in

- CPUs

AMD also gave us a brief update on 45nm, stating that they have successfully produced a SRAM test wafer at 45nm. It's very popular to produce a wafer full of SRAM chips as you're bringing up and validating any new process, since the circuits are simple enough to actually make the chips producable but complex enough to get useful feedback on your process from the test wafer.

AMD's 45nm SRAM test wafer follows a little over 3 months after Intel demonstrated a similar 45nm test wafer. The benchmark when producing a wafer of SRAM is how small you're able to produce each SRAM cell. At 45nm Intel was able to achieve a 0.346 square micron SRAM cell size compared to AMD's 0.370 square micron SRAM cells. Intel's advantage in SRAM cell size is nothing new, as they have been doing so in previous process technologies as well. The advantage in SRAM cell size is one reason why you often see Intel more eager to equip its CPUs with larger L2 caches; obviously with no on-die memory controller, Intel also often benefits much more from a larger L2 cache than AMD in the first place.

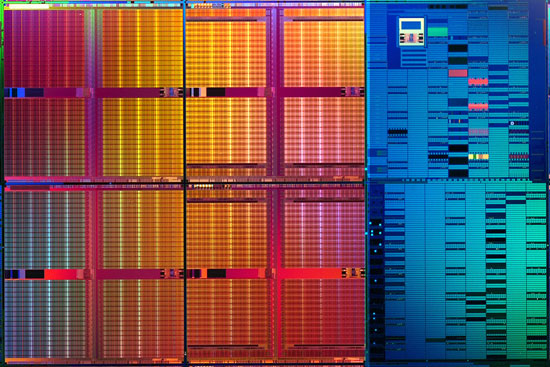

Intel's 45nm SRAM test vehicle - 0.346 sq micron cell size

Today's update had nothing to do with Socket-AM2 or AMD's transition to DDR2, but we do have some news with regards to that as well. As you've undoubtedly heard and maybe even seen elsewhere, AMD's AM2 platform has not been performing very well in development over these past couple of months. Just before IDF, AM2 samples were still performing lower than their Socket-939 counterparts, which was beginning to worry us and AMD's parters a bit. However we're excited to report that AM2 performance has finally started exceeding that of Socket-939. The performance gains we've been hearing and seeing are generally 5% or lower at the same clock speeds using DDR2-800, but it's still very early. The main point to take home is while the final verdict is still not out, AM2 is at least starting to look like more of an upgrade and not what we saw with Intel's DDR to DDR2 transition almost 2 years ago.

There's still a lot that AMD does have to give us however, including a more specific roadmap of what comes after their DDR2 transition. AMD's Phil Hester has publicly stated that once AM2 launches it will be more forthcoming with information on future architecture revisions, we can only hope so because over the past 12 months Intel has put the pressure on AMD to really start talking about the future.

The good news today is that AMD is truly growing as a company. By 2008 AMD hopes to be able to double its yearly shipments of microprocessors, and it's finally got manufacturing capacity to do just that. For the past few years AMD has held technological and performance advantages over Intel, now it's time for AMD to play catchup on the manufacturing side. AMD has a long way to go before being anywhere close to Intel's manufacturing abilities, but it is in a very good place today.

68 Comments

View All Comments

Viditor - Thursday, April 6, 2006 - link

Because it's their only dual core x86 server chip...so it's pretty much the only example possible.

You can extrapolate results by comparing Paxville to Nocona (since it's just a Nocona MCM...)

I'm confused here. I'm sure you're not saying that as both are at 65nm, Conroe will be smaller than Brisbane...that would be silly as it has double the cache. Also, if you look at current die pictures of AM2, you'll notice that the same amount of cache is significantly smaller on Rev F than it was on Rev E (i.e. AMD has drastically improved their cache density).

IIRC, this began with you repeating some of the Intel marketing stuff about MCMs being a much more economical way to produce chips, but the fact that Conroe wasn't using it was irrelevant (i.e. it wouldn't reduce their yields) because they are smaller...

As to AMD's yields, they have stated many times over the last 3 months that 65nm will START at the same yields that current 90nm chips enjoy (mature yields). They have even shown how this is possible with APM and given an example with their 90nm process which was close to mature yields at it's launch.

I disagreed with your comment about the ODMC making a difference. I don't believe there is anything inherent in the NetBurst uA that precludes it from being a true dual core (either with a shared cache or DCA)...except of course that Intel didn't plan for it. Therefore (as you say), for NetBurst chips, MCMs were the only possible way to go. IMHO, the "yield advantage" is just Intel's way of "making lemonade"...

I still see no reason why NGMA cores will fare any better with MCM than their NetBurst brethren did.

This brings up a last point...will AMD go MCM as well? Most of us are assuming that they will continue with DCA for their cores, but all of the Hammers have been DC designs since the very beginning. I have no idea as to whether or not the AMD Quad Cores are true quads or MCMs. If anybody knows for a fact one way or another, please post!

coldpower27 - Thursday, April 6, 2006 - link

I am not gonna have to take extrapolations using NetBurst architecture as a template as pretty much useless. The FSB bandwidth avaialble to Core Architecture will be significantly enhanced in comparison to what Paxville or Nocona has access to.The NetBurst Architecture is too bandwidth dependent to serve as a good indicator of how Core Architecture will react.

I am saying Intel will have an advantage with Allendale vs Brisbane 2 processors with equal amount of total LV2 cache. Not in relation to Conroe. With Conroe it is unknown as it would be a fairly mature product by that timeframe, so it's hard to compare yield between AMD and Intel.

The definition of mature yields has been vague to me at best, perhaps it means that entering into the 65nm process they will have equal to greater output then can be had on the mature 90nm process going out... Not an issue really for desktops till H1 2007 however. Indications look like AMD will try to concentrate on the server and mobile segements with their 65nm production.

"True Dual Core" your actually spouting that AMD propaganda??? Dual Core says there only has to be 2 cores, their isn't anything in the definition that limits it to a monolitic die vs MCM module. Presler is no less "true" then Toledo, maybe you should stick to the monolithic vs MCM argument instead of using vague terminology as "true".

It's common knowledge that a smaller die is easier to yield then a larger one on a given process, it simply a matter of more surface area for a defect to occur. Your opinion of the making lemonade part is jsut that your opinion which I don't agree with, NetBurst Dual Core designs wasn't amazing as it wasn't design to be a Dual Core that is true from what Intel has spoken on the subject, but the solution cranked out was an acceptable one for something that had no intention of moving to Dual Core.

There isn't a point in making a monolithic design for NetBurst now as Intel is moving to a more integrated design like AMD did, where the two cores work more closely like in Conroe with Shared LV2. Why spend resources to improve the old NetBurst Architecture, when you have sometihng much better in the works.

Well a surprise for you is that Tulsa the Xeon MP core will based based on Netburst MicroArchitecture and will have access to 16MB of Shared LV3 cache.

Can AMD go MCM at all? I mean with how closely their cores are working together with their ODMC shared between the two cores.

It won't matter in the end though, we'll get monolithic quad core designs out of Intel on the 45nm node when it's more economical to do so and hence having the ability for each core to work more closely with the other 3. The 65nm versions are just first interations to wet the peoples appetite for better quad cores as we go down the road.

I am not saying a MCM design is great for performance either, but it's important to see how adversely Core Architecture will be affected, since even going through a FSB that is 1.33GHZ is alot better then the 800MHZ FSB that Paxville's platform was stuck with. I am all for a monolithic die package Quad Core when economically feasable, but a MCM design in the meantime is an adequate solution to introduce Quad Core.

Viditor - Thursday, April 6, 2006 - link

Not for determining the penalty that MCM incurs it isn't...though it would be for determining the exact performance of Kentsfield (we haven't actually benched them yet).

It's true that Intel will be increassing the FSB from 800MHz to 1333MHz (an increase of 40%), but for quad core you will also be increasing the number of cores by 100%...

Sorry, but where does it "say" that? Both "Dual" and "Twin" mean 2...however Dual implies identical and connected while twin implies not connected but identical. Doesn't it make more sense and seem clearer to call an MCM a "twin" core for clarification?

We shall have to agree to disagree then...IMHO, the twin core solution did allow Intel to save a bit of face, but as their sales and reviews of twin core CPUs was so dismal, I would hardly call it acceptable.

That's assuming a single ODMC...just as Intel is going to a 2 FSB model, AMD could use a dual ODMC model on quad core. Then, all they would need is a cHT link between the cores (just as like it is between cores on current Opteron MP chips). This would solve a problem and create one.

1. Latency for cache coherency would increase, but only slightly

2. memory bandwidth would double per CPU

A main advantage over Intel though is that it would be a cHT link rather than arbitration through the FSB...just hypothesizing here.

MrKaz - Wednesday, April 5, 2006 - link

Yes but i still tell you the same:For each 1000 processor cores build intel sells 500 processors... half of production, is also a huge hit. I'm not saying AMD implementation is better...

Celeron is only 256kb cache not 512kb.

coldpower27 - Wednesday, April 5, 2006 - link

I was talking the Cedar mill revision, that will be released soon, right now they are still based on Prescott so 256KB yes, the Cedar Mill version will be 512kb.Intel sells 500 Dual Cores, or it could be 250 Dual Cores and 500 Single Cores, it depends on market needs.

her34 - Wednesday, April 5, 2006 - link

what's intel's total production capacity?logeater - Tuesday, April 4, 2006 - link

Poor AMD. All this spin doctoring has left them to dizzy to actually know what they are doing. The AM2 will struggle to get anywhere near Conroe if you are smart enough read between the lines.Time to take out my stocks in AMD and pump them into Intel me thinks. ;)

Viditor - Wednesday, April 5, 2006 - link

Cool...that'll be me on the other end of that transaction! :)

MrKaz - Wednesday, April 5, 2006 - link

Well Intel in the last 3 years has been lagging behind Intel. What’s the problem if Intel leaves AMD behind during some months or a year or two?That doesn’t mean Intel is superior. Right now still seems inferior to me...

MrKaz - Wednesday, April 5, 2006 - link

Well Intel in the last 3 years has been lagging behind AMD.