Introduction & Manufacturing

AMD held its spring Analyst Day on Thursday, and we were able to sit down and enjoy the webcast. While we fully expected to learn about AMD's next CPU architecture, K8L, we were pleasantly surprised to find a few unexpected extras. The event covered a huge swath of the computing industry in a manner that went just deep enough to leave us screaming for more. Unfortunately, we don't have all the answers we wanted today, but we do have some good ideas about what we'll be seeing in the near future about AMD's upcoming technology.

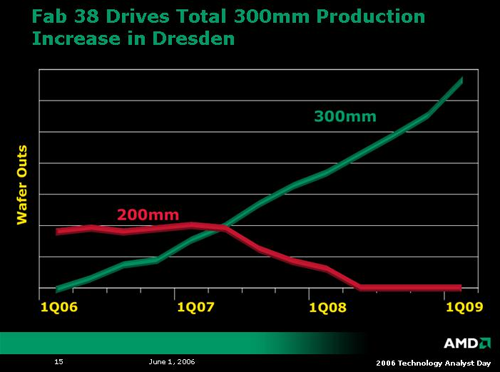

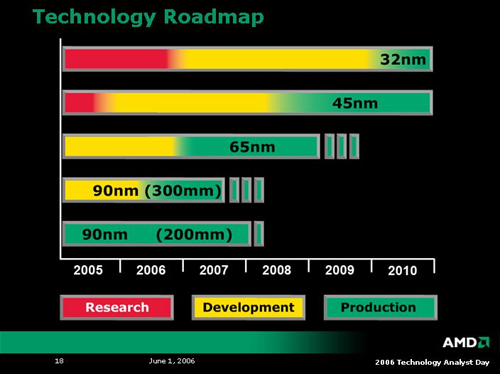

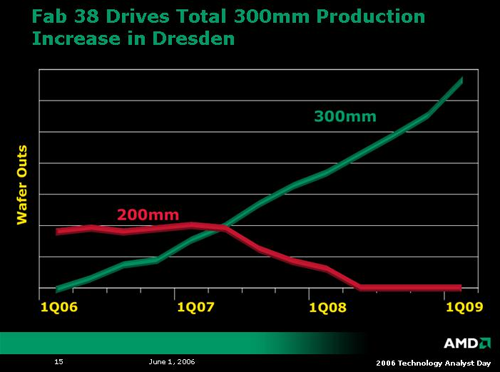

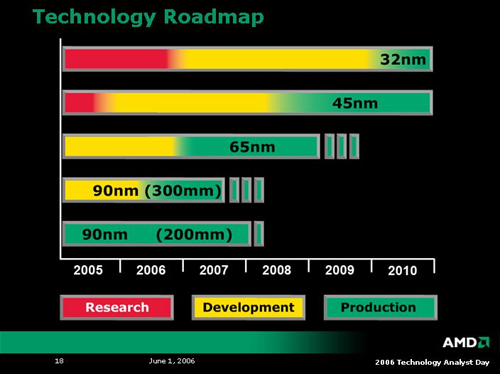

As could be expected, the day started off with an overview of AMD's fabrication strategies. In the near term, AMD is transitioning from 200mm wafers for its 90nm SOI process to 300mm wafers. This will help serve to get AMD up to speed with 300mm wafer before volume production of 65nm devices begins. As 200mm wafer production is phased out, 65nm processes will be ramping into full swing. AMD plans on an aggressive schedule for transitioning to the smaller process technology, and an even more aggressive schedule for pushing out 45nm technology after this product cycle. As of now, AMD plans to introduce production 45nm silicon only 18 months after 65nm hardware hits the market.

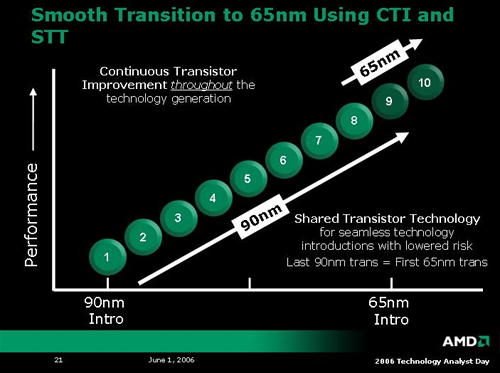

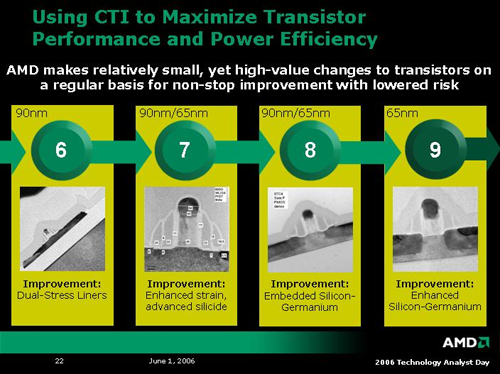

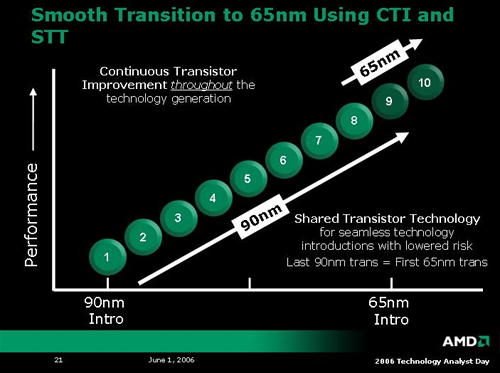

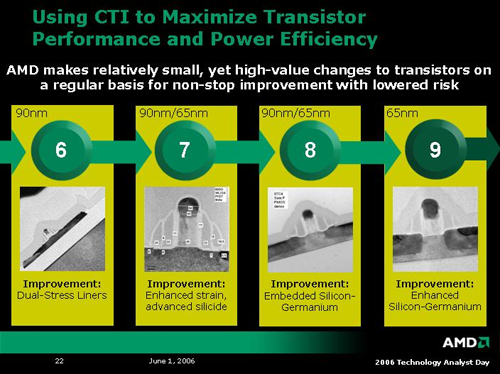

In moving to 65nm, AMD has adopted a strategy of constant improvement of its current transistor technology to ensure a smooth transition. The last generation 90nm parts will overlap the first generation 65nm parts, as many of the key features of their structures will be shared. AMD calls this Shared Transistor Technology and Continuous Transistor Improvement. As small improvements are made over the entire life cycle of a process, the final transition from one type of process to another is made much easier.

After AMD showed off a bunch of slides about how their fab is better than your fab, they started to touch on a few topics that really get our groove on: platform architecture. AMD introduced three new platform initiatives, and talked a little bit about their K8L architecture. First we'll talk about the direction AMD is moving with their platform technology.

AMD held its spring Analyst Day on Thursday, and we were able to sit down and enjoy the webcast. While we fully expected to learn about AMD's next CPU architecture, K8L, we were pleasantly surprised to find a few unexpected extras. The event covered a huge swath of the computing industry in a manner that went just deep enough to leave us screaming for more. Unfortunately, we don't have all the answers we wanted today, but we do have some good ideas about what we'll be seeing in the near future about AMD's upcoming technology.

As could be expected, the day started off with an overview of AMD's fabrication strategies. In the near term, AMD is transitioning from 200mm wafers for its 90nm SOI process to 300mm wafers. This will help serve to get AMD up to speed with 300mm wafer before volume production of 65nm devices begins. As 200mm wafer production is phased out, 65nm processes will be ramping into full swing. AMD plans on an aggressive schedule for transitioning to the smaller process technology, and an even more aggressive schedule for pushing out 45nm technology after this product cycle. As of now, AMD plans to introduce production 45nm silicon only 18 months after 65nm hardware hits the market.

In moving to 65nm, AMD has adopted a strategy of constant improvement of its current transistor technology to ensure a smooth transition. The last generation 90nm parts will overlap the first generation 65nm parts, as many of the key features of their structures will be shared. AMD calls this Shared Transistor Technology and Continuous Transistor Improvement. As small improvements are made over the entire life cycle of a process, the final transition from one type of process to another is made much easier.

After AMD showed off a bunch of slides about how their fab is better than your fab, they started to touch on a few topics that really get our groove on: platform architecture. AMD introduced three new platform initiatives, and talked a little bit about their K8L architecture. First we'll talk about the direction AMD is moving with their platform technology.

40 Comments

View All Comments

Squidward - Friday, June 2, 2006 - link

umm, that should be astronomicalthe message is clear... my typing has failed!

Hulk - Friday, June 2, 2006 - link

:|PrinceGaz - Saturday, June 3, 2006 - link

Conroe is already obsolete because K8L will grind it into the dirt. Anyone who buys a Core 2 Duo this year is wasting their money because AMD's K8L is better in every way. There's no point upgrading now unless you are stuck with a rubbish last-generation netburst processor like a Northwood or Prescott, because it's clear that K8L will totally annhilate Core 2 Duo and its successors. But if Intel fanbois want to waste their money on Core 2 Duo, that's fine. A little bit of competition from Intel before AMD strike their devestating counter-attack next year will ensure AMD don't cut corners in the K8L design.The best way to sum up the next year in CPUs is: Intel manage to gain a slight lead in the second half of 2006 and early 2007, but after that it will be AMD r0><0rs and Intel is teh su><0rs again!!!111

P.S. The above is not meant to be taken entirely seriously ;) though I do believe from what we've seen that K8L should be a bit ahead of what Intel have next year, if nothing else because of its integrated memory controller.

JumpingJack - Monday, February 5, 2007 - link

Really, where can I buy a K8L then??

MrKaz - Monday, June 5, 2006 - link

Tell me what does conroe, woodcrest and meron bring new to the market?Even the 5 years old amd hammer architecture presentation looks better than conroe, ..., ...

http://www.amd.com/us-en/assets/content_type/Downl...">http://www.amd.com/us-en/assets/content...ableAsse...

Darth Farter - Friday, June 2, 2006 - link

:|xTYBALTx - Friday, June 2, 2006 - link

Great article, but like everyone else I am interested in how 4x4 will improve gaming performance. Guess we'll have to wait and see.Calin - Monday, June 5, 2006 - link

More than two graphic cards will improve performance (over just two) only in the most insane resolutions (like 3000 by 2000 pixels). As for the use of four cores, there certainly exists - just not in the games right now. Even two cores won't bring a big boost in game performance - as of now. Who knows, maybe games ported from PS3 and XBox 360 will use them (hopefully)Regs - Friday, June 2, 2006 - link

I can kind of figure it out for myself but I wanted to make sure - what is cache coherency? Either way, Torrenza looks very interesting and very promising. Not only will AMD be delivering good competitive performance, but has a chance to unlock a whole new path in bringing a new standard through integrated computing.Hope you find out the goods for us Derek. Keep up the good work!

Ryan Smith - Friday, June 2, 2006 - link

To go with the shortest description, cache coherency is the catchall term for methods used to organize and inform multiple processors of cache changes in multiprocessor/multicore systems. Because both processors can work on the same data set at once, if one changes the data, the other needs to be intelligently informed about this, otherwise it will likely do something incorrectly.