Fall IDF 2006 - Day 1: 45/65nm, UMPC Update and Quad-Core

by Anand Shimpi & Larry Barber on September 26, 2006 5:03 PM EST- Posted in

- CPUs

Quad-Core in November

Intel's first quad-core processors will be released in Q4, and thus there's quite a bit of talk at IDF about Kenstfield (desktop) and Clovertown (server).

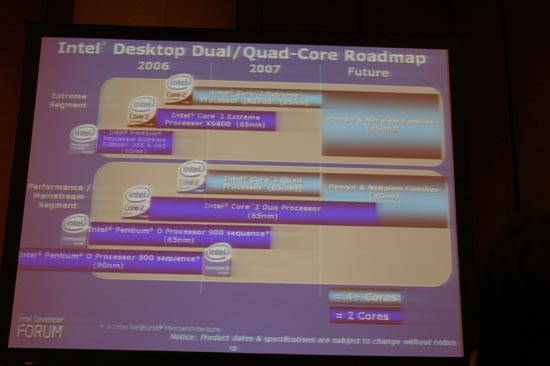

The first desktop quad-core processor will be the Core 2 Extreme QX6700 running at 2.66GHz, shipping in November of this year. Next year, Intel will introduce the Core 2 Quad Q6600 running at 2.40GHz. The transition to quad core CPUs will be much like the transition to dual-core CPUs in that for quite a while, the fastest processors will be offered in dual core flavors with slightly slower models available as quad-core.

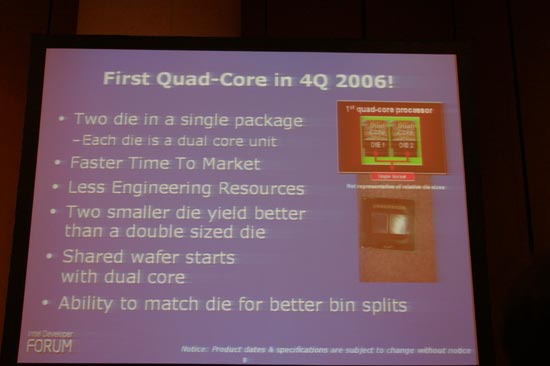

Just like Intel's Presler processors, Kentsfield will actually feature two individual die on a single package (two dual-core processors on one package):

While having two independent dual-core die isn't as fast as a single integrated quad-core die, we expect the performance penalty to be minimal in most applications (just as it was with the first dual core Intel chips). There are some benefits to using two independent dual-core die on a single package, which are highlighted above. They mostly relate to manufacturing and optimizing costs/production and thus won't be directly visible to the end user. If history repeats itself, we should expect Penryn (45nm) to be Intel's first single die quad-core desktop processor.

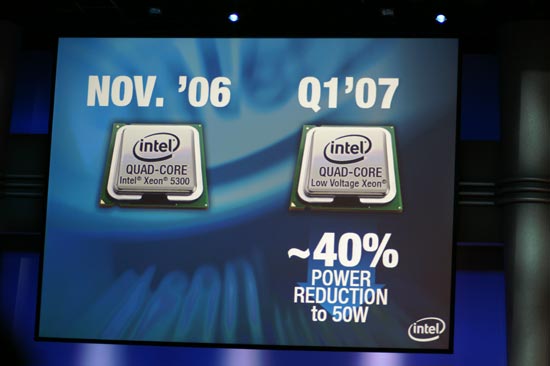

On the server side, Intel will launch its quad-core Xeon 5300 series in November alongside Kentsfield on the desktop. The Xeon 5300 will also be composed of two dual core die on a single package, codenamed Clovertown. Even more interesting is the Low Voltage quad-core Xeon due out in Q1 '07 that will offer four cores in a 50W power envelope.

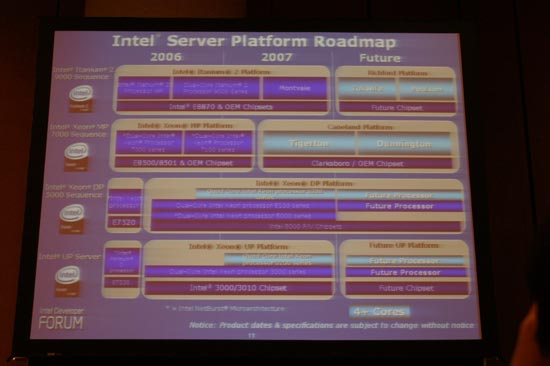

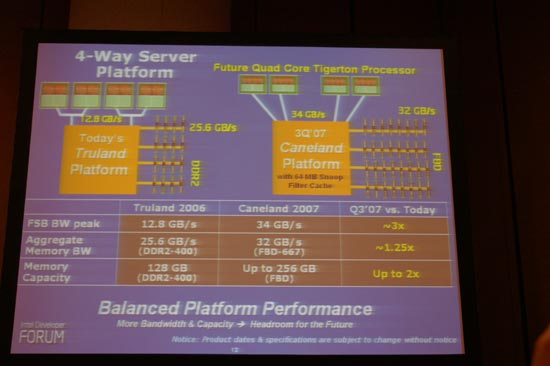

Next year Intel will also introduce its Caneland server platform for four socket servers, updating the Xeon MP platform to include support for Fully Buffered DIMM and four independent FSB interfaces - one for each socket.

While AMD's Direct Connect architecture is obviously a lot cleaner/simpler than requiring a MCH with four 64-bit FSB interfaces, until Intel eventually embraces an on-die MCH this is the best it can do. In order to help manage the CPU-to-CPU requests in the platform, Intel is also equipping the MCH with a 64MB Snoop Filter cache. Years ago Micron talked about equipping a chipset with an on-die L3 cache to help improve performance, and it's looking like Intel will be doing just that with its Caneland Xeon MP platform in Q3 '07.

12 Comments

View All Comments

gersson - Tuesday, September 26, 2006 - link

I would also like to make a generic statementPeteRoy - Tuesday, September 26, 2006 - link

Good to hear that there's still more to come.