AMD Athlon II X4 620 & 630: The First $99 Quad Core CPU

by Anand Lal Shimpi on September 16, 2009 12:00 AM EST- Posted in

- CPUs

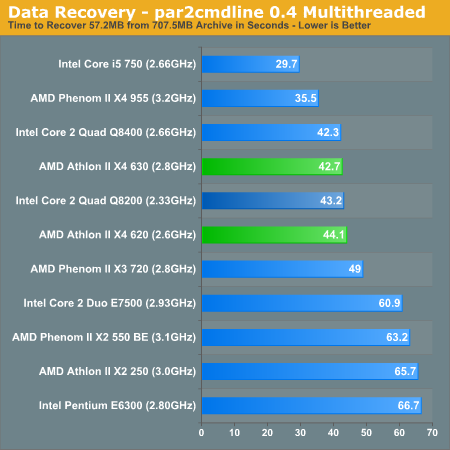

PAR2 Multithreaded Archive Recovery Performance

Par2 is an application used for reconstructing downloaded archives. It can generate parity data from a given archive and later use it to recover the archive

Chuchusoft took the source code of par2cmdline 0.4 and parallelized it using Intel’s Threading Building Blocks 2.1. The result is a version of par2cmdline that can spawn multiple threads to repair par2 archives. For this test we took a 708MB archive, corrupted nearly 60MB of it, and used the multithreaded par2cmdline to recover it. The scores reported are the repair and recover time in seconds.

Par2 is healthily threaded so the Athlon II X4s continue to do well here. The Q8200 inches by the 620, but for all intents and purposes it's the same speed as the $99 fighter from AMD.

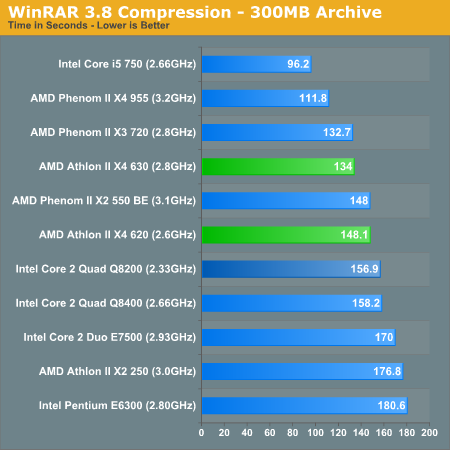

WinRAR - Archive Creation

Our WinRAR test simply takes 300MB of files and compresses them into a single RAR archive using the application's default settings. We're not doing anything exotic here, just looking at the impact of CPU performance on creating an archive:

The roles are reversed here, and all of the AMD architectures prove faster than their similarly priced Intel alternatives.

150 Comments

View All Comments

Chlorus - Wednesday, September 16, 2009 - link

He posted right after me...I'm kinda wondering if we should setup a drinking game or something each time he posts.strikeback03 - Wednesday, September 16, 2009 - link

Good idea, and everyone drinks when you spot a new alias.deputc26 - Wednesday, September 16, 2009 - link

I would absolutely love to see a die size comparison. That will give real information on how this chip can make AMD $$.Lokinhow - Wednesday, September 16, 2009 - link

there is a die size comparsion on the first page..P2 X4 = 258 mm2

A2 X4 = 169 mm2

A2 X2 = 117 mm2

C2Q 8xxx = 164 mm2

deputc26 - Wednesday, September 16, 2009 - link

Apparently I'm a moron. Don't know how I missed that unless it was added after initial publication as I read it right after it came out.Eeqmcsq - Wednesday, September 16, 2009 - link

Anand, how did you know whether or not your Athlon II X4s are harvested Denebs?Also, any idea why the Athon II X4s debut at such a high TDP with no L3? I'd think they'd be lower at 65w or at least 80w.

AMD, $100 quad cores is nice... BUT... where's the 45w quads???

Lokinhow - Wednesday, September 16, 2009 - link

I may be wrong, but..I think the high TDP is because we have both Propus and Deneb-Harvested Cores

The Athlon II based on Deneb probably have this 95W TDP, while the ones based on propus core have lower TDP.

I think they have only a few propus core to sell, so that's why they are selling harvesteds Denebs. When there wil have only Athlons II X4 propous based they'll rate it with a lower TDP.

Makes sense?

Spoelie - Wednesday, September 16, 2009 - link

Yes and noIt's a bit strange that the deneb die (630) consumes less power than the propus die (620) in idle if that theory was valid. During load the difference is just as much as the difference in clock speed would indicate. So if the 630 is indeed a deneb (care to rip the IHS of? ;)) then this means that propus is not by definition less power hungry than deneb.

Anand Lal Shimpi - Wednesday, September 16, 2009 - link

AMD specifically told us that our 620s are Propus samples, but that others may be Denebs. I'm not sure how to tell if you have a harvested Deneb just yet.Give AMD some time, I'm sure we'll see them down below 95W as the process matures for these dice.

Take care,

Anand

TA152H - Wednesday, September 16, 2009 - link

Anand,A couple of things. You mentioned the 'small' L2 cache being a problem on one of your benchmarks, but, it's actually twice as large as the one on the Phenom. I'm not sure if this was meant to be a comparison only with the Penryns, but it's a bit confusing.

Also, going back to the L2 cache, how can these possibly be harvested from Phenoms with a bad L3 cache. That would imply the Phenoms are built with 512K L2 cache, with half of it disabled. I really doubt this is the case. You CAN remove the L3, but how do they then double the L2 cache? This seems strange to me.

Based on the relatively poor overclocking potential of this chip, would you attribute that to the L2 cache? Does the L2 cache run with the same number of wait states as that of the Phenom? If so, that could prove to be the main reason for the lower overclocking potential. Any ideas on this?

Also, don't you think it's worth mentioning AMD's greatly superior IGPs, considering this product could easily find it's way in this platform rather often. The processor by itself does make sense, but, even if it didn't, the superior IGP platform still can make AMD processors somewhat attractive.