An AMD Update: Fab 36 Begins Shipments, Planning for 65nm and AM2 Performance

by Anand Lal Shimpi on April 4, 2006 11:00 AM EST- Posted in

- CPUs

AMD also gave us a brief update on 45nm, stating that they have successfully produced a SRAM test wafer at 45nm. It's very popular to produce a wafer full of SRAM chips as you're bringing up and validating any new process, since the circuits are simple enough to actually make the chips producable but complex enough to get useful feedback on your process from the test wafer.

AMD's 45nm SRAM test wafer follows a little over 3 months after Intel demonstrated a similar 45nm test wafer. The benchmark when producing a wafer of SRAM is how small you're able to produce each SRAM cell. At 45nm Intel was able to achieve a 0.346 square micron SRAM cell size compared to AMD's 0.370 square micron SRAM cells. Intel's advantage in SRAM cell size is nothing new, as they have been doing so in previous process technologies as well. The advantage in SRAM cell size is one reason why you often see Intel more eager to equip its CPUs with larger L2 caches; obviously with no on-die memory controller, Intel also often benefits much more from a larger L2 cache than AMD in the first place.

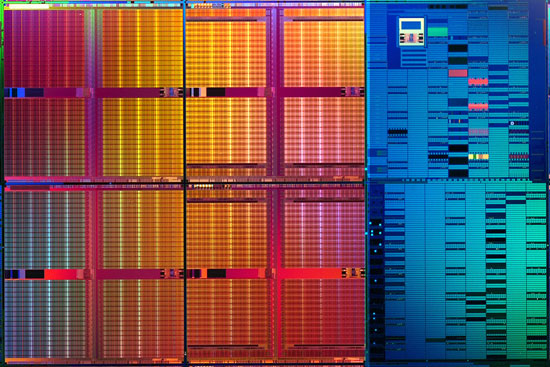

Intel's 45nm SRAM test vehicle - 0.346 sq micron cell size

Today's update had nothing to do with Socket-AM2 or AMD's transition to DDR2, but we do have some news with regards to that as well. As you've undoubtedly heard and maybe even seen elsewhere, AMD's AM2 platform has not been performing very well in development over these past couple of months. Just before IDF, AM2 samples were still performing lower than their Socket-939 counterparts, which was beginning to worry us and AMD's parters a bit. However we're excited to report that AM2 performance has finally started exceeding that of Socket-939. The performance gains we've been hearing and seeing are generally 5% or lower at the same clock speeds using DDR2-800, but it's still very early. The main point to take home is while the final verdict is still not out, AM2 is at least starting to look like more of an upgrade and not what we saw with Intel's DDR to DDR2 transition almost 2 years ago.

There's still a lot that AMD does have to give us however, including a more specific roadmap of what comes after their DDR2 transition. AMD's Phil Hester has publicly stated that once AM2 launches it will be more forthcoming with information on future architecture revisions, we can only hope so because over the past 12 months Intel has put the pressure on AMD to really start talking about the future.

The good news today is that AMD is truly growing as a company. By 2008 AMD hopes to be able to double its yearly shipments of microprocessors, and it's finally got manufacturing capacity to do just that. For the past few years AMD has held technological and performance advantages over Intel, now it's time for AMD to play catchup on the manufacturing side. AMD has a long way to go before being anywhere close to Intel's manufacturing abilities, but it is in a very good place today.

68 Comments

View All Comments

Homerr - Wednesday, April 5, 2006 - link

I keep looking but can't find when AM2 is supposed to be introduced. Can anyone enlighten me?Viditor - Wednesday, April 5, 2006 - link

6/6/06...

Toadster - Wednesday, April 5, 2006 - link

The grand opening of Fab 36 was mostly for media attention as the plant would not begin shipping revenue parts until Q1 of 2006. That sometime is today as AMD has just announced that Fab 36 is finally shipping revenue parts.Q1 ended last week LOL

hans007 - Wednesday, April 5, 2006 - link

i think a lot of it defeinitely is spin doctoring.another factor is that the dies are all single core dies which yield higher than dual core ones (since the dual core ones are not seperate like say presler if one of them is bad all of it is bad).

that said, the way amd make it sound it look slike their capacity will be greatly increased in the future because they can now make smallre chips. which is pretty stupid.

since even if they go to 65nm by the time 65nm is out everything intel makes will be dual core. so amd will have to sell everything dual core as well. so all the dies will be twice the size making the chips per wafer the same as it is now 90nm @ 300mm.

MrKaz - Wednesday, April 5, 2006 - link

That’s a good point.But this is only valid if Intel can get bad dual cores into single cores.

In the case of Presler, Intel for each 2 good chips get 1, so isn’t this the same of getting just one dual?

coldpower27 - Wednesday, April 5, 2006 - link

Yileding 2x 81mm2 dies is much easier then yielding AMDs single monolothic Toledo of 199mm2 or Windsor of 220mm2. If there is a defect in the processor core logic the Dual Core is completely useless and has to be thrown out. If it is the cache then they can make a lower cache Dual Core out of it.With Cedar Mill/Presler Intel is in a great position to address market needs as that core can be binned in 3 different SKU's.

Celeron D 35x Cedar Mill 512KB, disable part of the cache.

Pentium 4 6x1 Cedar Mill.

Pentium D Presler, 2 fully functioning Cedar Mill cores, from 2 different wafers even.

Viditor - Wednesday, April 5, 2006 - link

True...but it really hurts performance.

Honestly, if it was such an advantageous design financially then why would Intel design Conroe with a shared cache? I don't think the yields are affected as much as the spin doctors at Intel would have you believe...

coldpower27 - Wednesday, April 5, 2006 - link

It's not a big deal for Conroe or Allendale, those are 14x mm2 or 11x mm2 in die area, once you get back down to this level on 300mm wafers it's not too too bad.The NetBurst design had reached the end of it's life now, since it can't compete on performance effectively, it might as well rake in the advantage of reduced costs, good yeilds and flexibility. Since there isn't a ODMC, there isn't a reason to keep the dies together as NetBurst functions identically if the dies are seperate in Dual Core configuration.

The Dual Die implementation is an effective one, Intel will be using it for Kentsfield and Clovertown, on the 65nm process. Allowing them to put two Conroes or Woodcrests on a single MCM package. We'll see if it affects performance on Core Architecture negatively to the degree that it will uncompetitive. There is more then one way to extract performance.

Viditor - Wednesday, April 5, 2006 - link

So you're saying that once AMD gets to 65nm they will have better percentage yields because it will be a smaller die?

Can't say I agree here...

The only advantage to "joining" the dice (either through DCMA or shared cache) is cache coherency and avoiding the FSB.

Since Kentsfield will be for the desktop and Quad Core Opterons will be Socket F only, the one to watch will be Cloverton. Frankly it won't be the MCM as much as the lack of a P2P platform that will make Cloverton as ineffective as Paxville is...that said, if you look at the difference in core scaling on AMD vs Intel in the single to dual core market (or in this case DCMA vs MCM), you'll see exactly what I'm talking about.

coldpower27 - Thursday, April 6, 2006 - link

Like I said I am gonna wait and see on Clovertown, it might be an issue, though again it might not. Funny you choose the worst NetBurst Dual Core as your example..., I am just gonna wait till I see the results in the server market. Paxville has access to a much older platform however, so I don't really take results to be of much use.

No I don't think so, when AMD gets to 65nm, they won't beat Intel in the die size department, an optical shrink of Windsor to 65nm Brisbane, would be from 220mm2 to 132mm2. It would also depend if it's a straight shrink or if AMD adds more features and what not to their cores. I expect their yeilds to drop some from a mature 90nm SOI process, but total yield should be somewhat better.

I guess I should be more clear, the die sizes for Conroe/Allendale are fine as they are for Intel on a 65nm process that has been in production for at least 2Q.

How do you disagree again, as NetBurst doesn't have shared cache, not at the consumer level at least, so they communicate through the FSB anyway. Since the NetBurst design communicates through the FSB, the DUal Die implementation is fine...